半導体のさらなる高性能化を目指す最先端半導体パッケージ技術(アドバンスドパッケージ技術)の最新動向【LIVE配信・WEBセミナー】

~3D-IC・チップレット設計の最前線、エキシマVUV処理を利用した接着・接合技術~

★2025年12月19日WEBでオンライン開講。大阪大学 吉田氏、Cadence Design Systems 牧井氏、コジマイーデザインオフィス 小島氏、ウシオ電機株式会社 有本氏が、半導体のさらなる高性能化を目指す最先端半導体パッケージ技術(アドバンスドパッケージ技術)の最新動向~3D-IC・チップレット設計の最前線、接着・接合技術におけるVUV処理~】について解説する講座です。

■注目ポイント

★アドバンストパッケージング技術の背景、主要な技術課題と動向の解説にはじまり、チップレット・3DICの半導体設計向けの最新ソリューション、チップレット適用が進んでいるプロセッサー製品の設計標準言語とインターコネクト標準、半導体パッケージの集積を担う技術として期待されている表面処理について「エキシマVUV処理」をご紹介!

セミナー趣旨

■本セミナーの主題および状況(講師より)

★「ムーアの法則」の限界とAIの爆発的な需要を背景に、チップレットや2.5D/3D実装といったアドバンストパッケージング技術が半導体性能向上の鍵を握っています。

★生成AIの普及に伴い、データセンタや情報処理端末には高速化・大容量化・広帯域化が求められています。半導体の微細化について検討が進む一方で、半導体チップを高密度に実装することで、半導体チップの微細化と同等の性能向上をパッケージ基板として実現しようとするさらなる取り組みがなされています。

★チップレットとはチップ個片を意味する用語であり、チップレットへの分割とシステム統合により、ヘテロ集積(HI)を実現する設計手法を意味します。Monolithic Scalingの継続は高価であり、チップレットはScalingを持続させる経済的分割製造(サイズ、歩留まり、技術ノード)を可能にするソリューションであります。これには従来のMonolithic SoC設計技術に、半導体IPとしてチップレットを加えた統合SoC設計技術への進化が求められ、チップレット流通とチップレット統合を実現する国際標準規格の開発と普及が重要となります。

■注目ポイント

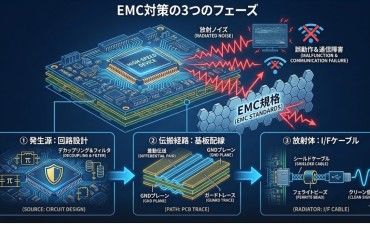

★アドバンストパッケージング技術の背景、高密度インターコネクト、熱問題、電源供給ネットワーク (PDN)、テスト技術、複数物理領域にわたる統合設計、チップレットエコシステムにおける標準化の促進といった主要な技術課題と動向を解説!

★チップレット・3DICの半導体設計向けの最新ソリューション、チップレット適用が進んでいるプロセッサー製品の設計標準言語とインターコネクト標準について詳説!

★半導体パッケージの集積を担う技術として期待されている表面処理について「エキシマVUV処理」を中心にご紹介!

習得できる知識

第1部

半導体パッケージングについて、政策、ビジネス、技術の観点で、現状と見通しを理解することができます。

第3部

プロセッサー製品の適用状況、設計標準言語、インターコネクト標準とチップレット検査の課題について学習できる。

第4部

・光を用いた表面処理技術

・ドライプロセス

・エキシマVUV処理

・大気圧プラズマ処理

・フラッシュランプアニール

セミナープログラム

【第1講】 アドバンストパッケージの基礎

【時間】 11:00-12:00

【講演主旨】

「ムーアの法則」の限界とAIの爆発的な需要を背景に、チップレットや2.5D/3D実装といったアドバンストパッケージング技術が半導体性能向上の鍵を握っています。

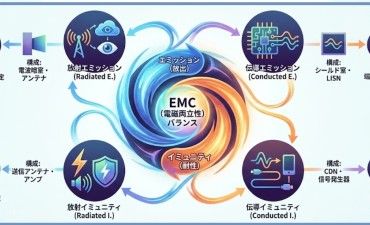

本講座では、これらの技術の背景に加えて、高密度インターコネクト、熱問題、電源供給ネットワーク (PDN)、テスト技術、複数物理領域にわたる統合設計、チップレットエコシステムにおける標準化の促進、といった主要な技術課題と動向を解説します。

これらの課題に対する革新的な解決策が、今後の半導体産業とAIの進化をどのように牽引していくか、その見通しを深掘りします。

【プログラム】

○アドバンストパッケージ・チップレットの背景

○技術動向

○今後の見通し

【質疑応答】

【キーワード】

チップレット、アドバンストパッケージ、インターコネクト、PDN、光電融合

【講演のポイント】

半導体のことをよくご存じない方でもわかるように、今般の半導体パッケージングについて、政策、ビジネス、技術の観点で、現状と見通しをわかりやすく解説します。

【第2講】 3D-IC・チップレット設計の最前線:先進パッケージングを加速するケイデンスの統合ソリューション

【時間】 13:00-14:15

【講演主旨】

近年、AIやHPC、車載システムの進展により、より高性能かつ低消費電力なSoCの開発が求められています。

しかし、従来の2D設計では、トランジスタ密度の限界や配線遅延、消費電力の増加といった課題が顕在化しており、ムーアの法則の持続が困難になりつつあります。こうした背景から、複数のチップレットを垂直方向に積層し、短距離・高帯域で接続する3D IC技術が注目されています。3D ICは、設計の自由度を高めると同時に、性能向上と省電力化の両立を可能にする次世代のアーキテクチャとして、今後の半導体開発において不可欠な技術となりつつあります。

本講演では、ケイデンスが提供する3D IC設計ソリューションを取り上げ、設計探索、物理設計、解析、サインオフまでを統合的に支援する最新技術をご紹介します。また、ファウンドリとの連携事例や、AI設計との融合による開発加速手法についても解説し、次世代半導体設計の潮流を示します。

【プログラム】

1. 半導体業界のトレンドとチップレット・3DICの概要

・Chiplet/3DICのチャレンジと必要な技術要素

2. チップレット・3DIC設計に必要な要素技術

・ケイデンスの提供しているChiplet/3DIC設計プラットフォーム紹介

・チッププラニング技術

・解析技術

・チップ実装技術

3. チップレット・3DICに必要なファウンドリとの協業

・ファウンドリとの協業内容と今後

4. サマリ

・これからの半導体設計に必要な技術

・ケイデンスの技術ロードマップ

・チップレット・3DIC設計の今後

【質疑応答】

【キーワード】

半導体、チップレット、積層チップ、EDA、設計

【講演のポイント】

EDAベンダーが提供しているチップレット・3DICの半導体設計向けの最新ソリューションをご覧いただけます。

また、チップレット設計における課題と必要な要素技術を理解いただけます。

【第3講】 チップレット設計の現状とその標準化について

【時間】 14:25-15:40

【講師】コジマイーデザインオフィス 代表 小島 智 氏

【講演主旨】

チップレットとはチップ個片を意味する用語であり、チップレットへの分割とシステム統合により、ヘテロ集積(HI)を実現する設計手法を意味する。Monolithic Scalingの継続は高価であり、チップレットはScalingを持続させる経済的分割製造(サイズ、歩留まり、技術ノード)を可能にするソリューションである。これには従来のMonolithic SoC設計技術に、半導体IPとしてチップレットを加えた統合SoC設計技術への進化が求められ、チップレット流通とチップレット統合を実現する国際標準規格の開発と普及が重要となる。

チップレット適用が進んでいるプロセッサー製品の状況を述べ、設計標準言語とインターコネクト標準について詳しく説明する。また、チップレット検査の課題についても簡単に触れる。

【プログラム】

1. 背景

1.1 チップレットの位置付け

1.2 各国政府の取組(米国Chips法、EU Chips法、国内ASRAなど)

2. 製品への適用状況

2.1 プロセッサーへの適用

2.2 製品の適用例 (Nvidia、AMD、Intelなど)

2.3 光チップレットの取組

3. チップレット設計技術

3.1 統合SoC設計環境

3.2 設計標準言語(3DBlox、CDXML)について

4. インターコネクト標準

4.1 標準化動向について

4.2 UCIe規格について

5. チップレット検査の課題について

【質疑応答】

【キーワード】

UCIe、3DBlox、ヘテロ集積(HI)、光チップレット、ASRA、Chiplet Summitt

【講演のポイント】

チップレットは、エレクトロニクス分野で大きな注目を浴びており、Buzzwordとなっている。多くのステークホルダーが関わり、立場により見方が大きく異なる。特にパッケージ実装のプロセスと材料に偏った見方が多く散見される。鳥瞰的視点でこの技術を眺めて全体を理解した上、チップレット設計技術について深く理解することができる。

【第4講】 アドバンスドパッケージ向け表面処理技術のご紹介

【時間】 15:50-17:05

【講演主旨】

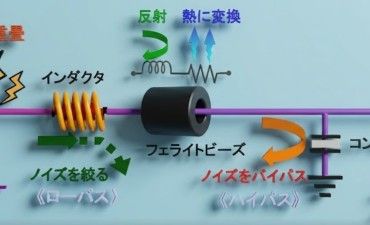

生成AIの普及に伴い、データセンタや情報処理端末には高速化・大容量化・広帯域化が求められている。半導体の微細化について検討が進む一方で、半導体チップを高密度に実装することで、半導体チップの微細化と同等の性能向上をパッケージ基板として実現しようとするさらなる取り組みがなされている。本講演では、半導体パッケージの集積を担う技術として期待されている表面処理について、エキシマVUV処理を中心にご紹介する。

【プログラム】

・半導体パッケージ基板で提案する光ソリューション

・ USHIOの表面処理技術① 大気圧プラズマ

・ USHIOの表面処理技術② エキシマVUV

・ エキシマVUV処理を利用した接着・接合技術

・ USHIOの表面処理技術③ FLAによる光加熱

【質疑応答】

【キーワード】

表面処理,表面改質,パッケージ基板,先端半導体パッケージ

【講演のポイント】

光のリーディングカンパニーとして,ウシオ電機の製品は精密洗浄,材料に機能性を持たせる表面改質,低ダメージのアッシングなど表面処理の分野で多様な用途に応じて活用されております.

セミナー講師

第1部 大阪大学 産業科学研究所 F3D実装協働研究所 吉田 浩芳 氏

第2部 Cadence Design Systems ATX/Director 牧井 徹 氏

第3部 コジマイーデザインオフィス 代表 小島 智 氏

第4部 ウシオ電機株式会社 光プロセスGBU 要素開発部 プロセス開発課 有本 太郎 氏

セミナー受講料

【1名の場合】60,500円(税込、テキスト費用を含む)

2名以上は一人につき、16,500円が加算されます。

主催者

開催場所

全国