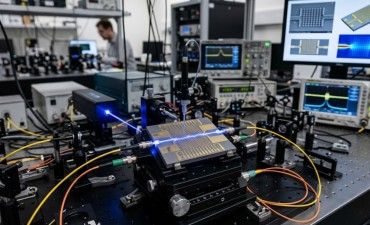

半導体高集積化技術:先端リソグラフィ技術の開発動向と先端パッケージ技術の基礎・最新の微細再配線層(RDL)形成プロセス【LIVE配信・WEBセミナー】

★2026年1月28日WEBでオンライン開講。Eリソリサーチ 遠藤氏が、【半導体高集積化技術:先端リソグラフィ技術の開発動向と先端パッケージ技術の基礎・最新の微細再配線層(RDL)形成プロセス】について解説する講座です。

■注目ポイント

★半導体高集積化技術の両輪である【先端リソグラフィ技術】と【先端パッケージ技術】について基礎から最新技術動向まで網羅的に解説!

セミナー趣旨

■本セミナーの主題および状況(講師より)

★生成AIの進化とともに大量のデータ処理がデータセンターに集まり、その処理を超高速度に低消費電力、低損失に行うために半導体チップに対して大きな要求がなされています。

★このため微細化(先端リソグラフィ;半導体前工程)に加えて、集積化を促進する積層構造(先端パッケージ;半導体後工程)がクローズアップされています。

■注目ポイント

★先端リソグラフィ技術について「EUVリソグラフィ/EUVレジスト」を中心に「ダブル/マルチパターニング」、「自己組織化(DSA)リソグラフィ」について解説!

★先端パッケージ技術について「2.5Dパッケージ技術(CoWoS等)」の特徴と課題、「厚膜レジストの特性等」を解説!

★今後の微細化が求められるチップ間接続のキープロセスである「再配線層(RDL)形成プロセス」の現状と要求・課題、今後の展望を解説!

【講演主旨】

生成AIの進化とともに大量のデータ処理がデータセンターに集まり、その処理を超高速度に低消費電力、低損失に行うために半導体チップに対して大きな要求がなされています。このため微細化(先端リソグラフィ;半導体前工程)に加えて、集積化を促進する積層構造(先端パッケージ;半導体後工程)がクローズアップされています。本講演では両技術のロードマップを紹介した後、先ず先端リソグラフィ技術の開発動向を述べます。ここでは最先端工程で用いられているEUVリソグラフィ/EUVレジストを中心に、ダブル/マルチパターニング、自己組織化(DSA)リソグラフィについて解説します。続いて先端パッケージ技術の基礎を述べます。ここでは中核技術である2.5Dパッケージ技術(CoWoS等)の特徴と課題、厚膜レジストの特性等を解説します。最後に今後の微細化が求められるチップ間接続のキープロセスである再配線層(RDL)形成プロセスの現状と要求・課題、今後の展望を解説します。

習得できる知識

1)先端リソグラフィ技術の動向

2)先端半導体パッケージ技術の基礎

3)微細再配線層(RDL)形成プロセスの動向

セミナープログラム

【プログラム】

1. ロードマップ

1.1 リソグラフィ技術のロードマップ

1.2 半導体パッケージ技術のロードマップ

1.3 最先端デバイスの動向

2. 先端リソグラフィ技術の開発動向

2.1 ダブル/マルチパターニング

2.1.1 ダブル/マルチパターニングの基本と課題

2.1.2 リソーエッチ(LE)プロセス

2.1.3 セルフアラインド(SA)プロセス

2.2 EUVリソグラフィ

2.2.1 EUVリソグラフィの特徴

2.2.2 EUVリソグラフィの基本と課題

2.2.3 高NA EUVリソグラフィの現状と課題

2.2.4 EUVレジスト

2.2.4.1 EUVレジストの基本

2.2.4.2 EUVレジストの課題と対策

2.2.4.2.1 感度/解像度/ラフネスのトレードオフ

2.2.4.2.2 ランダム欠陥(Stochastic Effects)

2.2.4.3 EUVレジストの動向

2.2.4.3.1 ネガレジストプロセス

2.2.4.3.2 ポリマーバウンド酸発生剤を用いる化学増幅型レジスト

2.2.4.4 EUVメタルレジスト

2.2.4.5 EUVメタルドライレジストプロセス

2.3 自己組織化(DSA)リソグラフィ

2.3.1 グラフォエピタキシー

2.3.2 ケミカルエピタキシー

3. 先端半導体パッケージ技術の基礎

3.1 Flip-Chip BGA(FC-BGA)

3.2 Fan-Out Wafer-Level Package (FOWLP)

3.2.1 Integrated Fan-Out(InFO)

3.3 2.5D パッケージ技術

3.3.1 シリコンインターポーザー型(CoWoS-S、I-CubeS)

3.3.2 有機インターポーザー型(CoWoS-R、R-Cube)

3.3.3 シリコンブリッジ型(CoWoS-L、EMIB、I-CubeE)

3.4 3DIC

3.4.1 ハイブリッドボンディング

3.5 厚膜レジストの特性

3.5.1 厚膜レジストの用途

3.5.2 厚膜レジストの性能と課題

3.5.3 厚膜レジストの材料

4. 微細再配線層(RDL)形成プロセスの現状と要求・課題、今後の展望

4.1 再配線層のロードマップ

4.2 SAP方式

4.3 ダマシンCMP方式

4.3.1 ダマシンCMP用パターン形成方法

4.3.2 有機誘電体材料の必要特性

【質疑応答】

【キーワード】

リソグラフィ、レジスト、EUVリソグラフィ、EUVレジスト、ダブルパターニング、マルチパターニング、自己組織化(DSA)リソグラフィ、パッケージ、CoWoS、厚膜レジスト、ハブリッドボンディング、再配線層(RDL)、有機誘電体材料

【講演のポイント】

半導体高集積化技術の両輪である先端リソグラフィ技術と先端パッケージ技術について、基礎から最新技術動向まで把握できます。最新のロードマップにおける位置づけ、ビジネス動向を確認できます。

セミナー講師

Eリソリサーチ 代表 遠藤 政孝 氏

セミナー受講料

【1名の場合】49,500円(税込、テキスト費用を含む)

2名以上は一人につき、16,500円が加算されます。

主催者

開催場所

全国