チップレット実装の基礎とそのテスト手法及び評価技術

セミナー趣旨

チップレットは多数のチップを1パッケージに集積する技術であり、従来からのチップ単体テスト手法だけでなく、チップレットのための新たなテスト手法が必要となる。

本セミナーでは、電子回路テストの基礎技術を紹介したうえで、チップレットの概要、チップレットテストの考え方、真のKGD(Known Good Die)選別のためのテスト手法、ウェーハプローブの課題と最新動向、インターポーザのテスト、システムレベルテスト、SDC(サイレントデータ破損)、チップレット相互接続テストのためのバウンダリスキャンとIEEE1838規格、TSV接続障害リペア方式とUCIe規格、ハイブリッドボンディングなど超狭ピッチTSV接続を評価するための新たな計測方法などを紹介する。

本セミナーを受講することで、・電子回路テストの基礎知識、・チップレットの概要、・チップレットテストの考え方と動向、・バウンダリスキャンの基礎知識とチップレットテスト規格 IEEE 1838、・TSV接続障害回避技術とUCIe規格、・アナログバウダリスキャンによるTSV接続の新しい評価技術の知識が得られます。

セミナープログラム

1 はじめに

1.1 講師紹介

1.2 富士通の大型計算機のテクノロジーとテスト技術の歩み

1.3 バウンダリスキャンの採用と普及活動

2 チップレットの概要

2.1 チップレットとは

2.2 なぜ、今チップレットなのか

2.3 ムーア則とスケーリング則

2.4 チップレットの効果

2.5 チップレットの適用事例

2.6 チップレット実装の例

2.7 インターポーザの動向

2.8 インターポーザの事例

3 チップレットテストの動向

3.1 チップレット集積のテストフロー

3.2 KGD(Known Good Die)の重要性

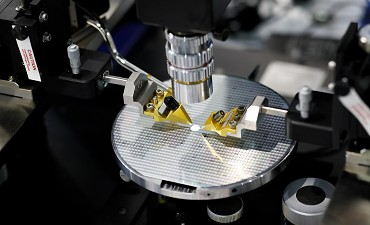

3.3 ウェーハプローブテスト

3.4 真のKGD選別とIntelの戦略

3.5 積層ダイテストとファイナルテスト

3.6 システムレベルテストSLT

3.7 ICの構造テストと機能テスト

3.8 ATEとSLTのテストメカニズム

3.9 サイレントデータ破損(Silent Data Corruptions)

3.10 インターポーザのテスト(接触方式と非接触方式)

3.11 EBテスタとCMOS容量イメージセンサによる非接触テスト

3.12 TSMCのPGD(Pritty-Good-Die)テスト

4 チップレット間のインターコネクションテスト

4.1 チップレットは小さな実装ボード

4.2 実装ボードの製造試験工程

4.3 実装ボード・チップレットの機能テストと構造テスト

4.4 バウンダリスキャンの基礎知識

4.5 IEEE1149.1バウンダリスキャンテスト回路

4.6 バウンダリスキャンテストによるはんだ接続不良検出動作例

4.7 オープンショートテストパターン

4.8 ロジック−メモリ間のインターコネクションテスト

4.9 チップレットテスト規格IEEE1838とチップ間相互接続テスト

4.10 チップ積層後のIEEE1838 FPPによる各チップのロジックテスト

4.11 チップ積層後のTSV接続障害復旧方式とUCIe規格

4.12 Structural Test〜ボードテストとICテストでの違いカラ〜

4.13 ポストボンドテスト方式の学会発表例

4.14 TSMCのチップレットテスト事例

4.15 策定中のチップレット規格IEEE P3405 Chiplet Interconnect Test & Repair

4.16 進化するバウンダリスキャン関連規格

5 TSVの接続品質評価技術

5.1 3D-ICのチップ間接続(TSV、ハイブリッドボンディング)の高密度化と課題

5.2 TSV接合での欠陥と相互接続障害

5.3 TSV評価解析技術の例(断面観察、X 線 CT 画像検査、電気的評価)

5.4 従来評価技術(デイジーチェイン、ケルビン計測)の問題点…2端子法と4端子法

5.5 TSV接続評価時のアウトライヤ検出の重要性

5.6 TSVの個別抵抗計測による効果

5.7 アナログバウンダリスキャンIEEE1149.4による精密微少抵抗個別計測

5.8 従来のIEEE1149.4標準抵抗計測法の問題点と解決案

5.9 真のTSV個別4端子計測法の実現

5.10 TSV計測回路の3D-ICへの実装例

5.11 新評価方式の適用提案

6 Q&A

セミナー講師

亀山修一(かめやましゅういち) 氏

愛媛大学大学院 理工学研究科 客員教授(博士(工学)) / 技術士(電気電子部門)

<経歴、等>

1972 年、富士通株式会社に入社以来、一貫して生産技術部門でサーバー/スパコン等の電子回路の試験技術/試験設備の開発に従事、2017 年退職。

現在、愛媛大学客員教授、JEITA 3D 半導体モジュール WG メンバ、エレクトロニクス実装学会の学会誌編集委員/3D チップレット研究会委員、ミニマルファブ推進機構アドバイザ、富士通技術士会顧問、バウンダリスキャン協会代表、半導体関連企業等のコンサル、セミナー講師、亀山技術士代表。

IEEE、エレクトロニクス実装学会、電子情報通信学会、日本技術士会等の会員。

著書:バウンダリスキャンハンドブック(青山社、監訳)、Three-Dimensional Integration of Semiconductors (Springer、共著)ほか。

セミナー受講料

お1人様受講の場合 51,700円[税込]/1名

1口でお申込の場合 66,000円[税込]/1口(3名まで受講可能)

受講について

- 本セミナーの受講にあたっての推奨環境は「Zoom」に依存しますので、ご自分の環境が対応しているか、お申込み前にZoomのテストミーティング(http://zoom.us/test)にアクセスできることをご確認下さい。

- インターネット経由でのライブ中継ため、回線状態などにより、画像や音声が乱れる場合があります。講義の中断、さらには、再接続後の再開もありますが、予めご了承ください。

- 受講中の録音・撮影等は固くお断りいたします。

受講料

51,700円(税込)/人