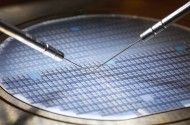

半導体メモリ(DRAM・NANDFlashメモリ)の製造プロセス技術、デバイス技術およびその動向

半導体メモリ(DRAM・NAND Flashメモリ)の構造・動作原理・特徴から製造方法、技術動向、プロセスや微細化の課題、今後の展望まで、2時間半で網羅的に解説!

セミナー趣旨

半導体デバイスの市場規模は現在100兆円に近づき、2030年には150兆円にもなるとも言われています。その大部分を占める半導体集積回路デバイス(LSI)は、私達の生活に無くてはならないものになりました。その一角を担う半導体メモリの代表であるDRAMとNAND Flashメモリ、それぞれの誕生(発明)、動作原理、変革について解説します。また、それらの構造と製造プロセス技術の全体像(プロセスフロー)を、3次元で表現した構造図を使い解説します。最後に、ビット密度(データの密度)向上、微細化、性能向上のためのプロセス技術、デバイス技術的な課題、チャレンジについて解説し、それらの今後の展望を主要な国際会議での発表を引用し解説します。

受講対象・レベル

・本テーマに興味のある方

・半導体デバイスメーカーの1~2年目社員の方

・半導体に関わる材料メーカーの方

・半導体に関わる部品メーカーの方

・半導体製造装置メーカーの方

習得できる知識

・DRAMの動作原理、特徴

・DRAMの製造方法

・DRAMの技術動向と展望

・NAND Flashメモリの動作原理、特徴

・NAND Flashメモリの製造方法

・NAND Flashメモリの技術動向と展望

セミナープログラム

1.DRAM概要

1-1.DRAMの用途

1-2.DRAMの誕生

1-3.DRAMの動作原理

1-4.DRAMの特徴

1-5.DRAMの構造

2.DRAMの製造方法(プロセスフロー)

〇各工程を三次元の図により解説します。

2-1.STI形成

2-2.Word Line形成(アクセストランジスタ形成)

2-3.Bit Contact形成

2-4.Bit Line形成

2-5.Storage Contact形成

2-6.Capacitor形成

2-7.配線形成

3.DRAMの課題

3-1.DRAMのプロセス課題

3-2.DRAMの微細化の課題

4.DRAMの技術動向

4-1.主要学会におけるDRAM技術

4-2.DRAMの今後の展望

5.DRAMの技術のまとめ

6.NAND Flashメモリ概要

6-1.NAND Flashメモリの用途

6-2.NAND Flashメモリの誕生

6-3.NAND Flashメモリの動作原理

6-4.NAND Flashメモリの特徴

6-5.NAND Flashメモリの構造

7.NAND Flashメモリの製造方法(プロセスフロー)

〇各工程を三次元の図により解説します。

7-1.積層スタック形成

7-2.積層スタックの階段形状形成

7-3.Memory Hole形成

7-4.Slit形成

7-5.メタルリプレース(Word Line形成)

7-6.Contact形成

7-7.Bit Line形成

8.NAND Flashメモリの課題

8-1.NAND Flashメモリのプロセス課題

8-2.NAND Flashメモリのビット密度向上の課題

9.NAND Flashメモリの技術動向

9-1.主要学会におけるNAND Flashメモリ技術

9-2.NAND Flashメモリの今後の展望

10.NAND Flashメモリの技術のまとめ

<終了後、質疑応答>

*途中、小休憩を挟みます。

■講演中のキーワード

DRAM、NAND Flashメモリ、製造プロセス技術、プロセスインテグレーション、デバイス技術

セミナー講師

ワイドヴィル 代表 廣田 良浩 氏

■ご経歴

・京都工芸繊維大学、大学院修士課程修了

・三洋電機株式会社(半導体事業本部)

・住友金属工業株式会社(未来技術研究所)

・イノテック株式会社

・東京エレクトロン株式会社(プロセスインテグレーションセンター、SPA開発部、

先端プロセス開発センター、プロセスインテグレーション部、デバイス技術企画部)

■ご専門および得意な分野・ご研究

MOS半導体デバイス技術・プロセスインテグレーション技術

■本テーマ関連学協会での活動

・一社)電子デバイス産業協会

・公社)精密工学会、CMPプラナリゼーション委員会とその応用技術専門委員会

・International Conference on Electronics Packaging and Hybride Bonding Symposium

・関西コンバーティングものづくり研究会

セミナー受講料

【オンライン受講(見逃し視聴なし)】:1名 36,300円(税込(消費税10%)、資料付)

*1社2名以上同時申込の場合、1名につき25,300円

【オンライン受講(見逃し視聴あり)】:1名 41,800円(税込(消費税10%)、資料付)

*1社2名以上同時申込の場合、1名につき30,800円

*学校法人割引:学生、教員のご参加は受講料50%割引。

主催者

開催場所

全国

受講について

- 配布資料はPDF等のデータで送付予定です。受取方法はメールでご案内致します。

(開催1週前~前日までには送付致します)

※準備の都合上、開催1営業日前の12:00までにお申し込みをお願い致します。

(土、日、祝日は営業日としてカウント致しません。) - 受講にあたってこちらをご確認の上、お申し込みください。

- Zoomを使用したオンラインセミナーです

→環境の確認についてこちらからご確認ください - 申込み時に(見逃し視聴有り)を選択された方は、見逃し視聴が可能です

→こちらをご確認ください