以下の類似セミナーへのお申込みをご検討ください。

3D-NANDフラッシュメモリの製造技術を用いた

微細限界の克服

平面型トランジスタの微細化限界を克服する、新しい積層型論理回路の開発技術について第一人者が丁寧に解説します!

講師

湘南工科大学 工学部 情報工学科 教授 博士(工学) 渡辺 重佳 先生

【講師紹介】

1979年 東芝入社。以来26年間LSIの研究開発に従事。東芝在籍中はフラッシュメモリの発明者である舛岡富士雄先生の直接の指導を受けた。

2005年10月より、湘南工科大学情報工学科に勤務。LSI、ハードウェア関連の教育、研究を行っている。

2015年以降 本セミナーで講演する積層ロジックLSIの研究に注力している。

受講料

1名41,040円(税込(消費税8%)、資料付)

*1社2名以上同時申込の場合 、1名につき30,240円

*学校法人割引 ;学生、教員のご参加は受講料50%割引。

セミナーポイント

LSIは過去ムーアの法則にしたがって平面型トランジスタの微細化が進み、大容量化、低コスト化、高速化、低消費電力化が着実に進められてきた。この平面型トランジスタの微細化もショートチャネル効果等のため近年限界に近付いている。本講演ではまず現在の平面型トランジスタを用いた平面型論理回路の設計法とその課題について述べる。

次にこの課題を解決するために提案された平面型論理回路を縦方向に積層した積層型論理回路について述べ、最後に講演者が独自に考案、提案した3D−NANDフラッシュメモリの製造技術を用いた新しい積層型論理回路について解説する。

新しい積層型論理回路は3D−NANDフラッシュメモリの製造技術を用いている為、低コストで、ムーアの法則、スケーリング則の限界を克服できる可能性を秘めている。本講演では講演プログラムに示した幾つかの論理回路で新しい積層型論理回路の実現可能性について説明する。

■ この講座を受講して得られる情報・知見:

*ムーアの法則、スケーリング則の限界を克服できるLSIの新しい候補を知ることができる。

*新たなLSIの設計法、製造技術の可能性について知ることができる。

■ 想定する受講対象:

電気・IT・半導体製造装置関連企業の方、経営コンサルタント、LSIを中心とした電気電子・情報関連の研究者、教員、学生等。

セミナー内容

1 ムーアの法則の限界

1.1 平面型トランジスタを用いたLSIの特徴

1.2 スケーリング則によるLSIの大容量化、低コスト化

2 平面型トランジスタを用いた積層型論理回路の取り組み

2.1 ワイヤボンディング方式

2.2 TSV方式

2.3 平面型トランジスタを用いた積層型論理回路の限界

3 3D−NANDフラッシュメモリの製造技術

3.1 3D−NANDフラッシュメモリとは

3.2 3D−NANDフラッシュメモリの製造技術の特徴

4 低コスト積層型ロジックLSI回路とは

4.1 Fe−FETとは

4.2 低コスト積層型ロジックLSI回路の基本構成

4.3 低コスト積層型ロジックLSI回路による低コスト化

5 低コスト積層型ロジックLSI回路の応用

5.1 組み合わせ回路

5.2 順序回路

5.3 LUT方式

5.4 FPGAへの応用

6 将来展望

6.1 低コスト積層型ロジックLSI回路によるムーアの法則の限界の克服

6.2 低コスト積層型ロジックLSI回路によるスケーリング則の限界の克服

<質疑応答>

※セミナーに申し込むにはものづくりドットコム会員登録が必要です

開催日時

12:30 ~

受講料

41,040円(税込)/人

※本文中に提示された主催者の割引は申込後に適用されます

※銀行振込

開催場所

東京都

【江戸川区】タワーホール船堀

【地下鉄】船堀駅

主催者

キーワード

半導体技術

※セミナーに申し込むにはものづくりドットコム会員登録が必要です

開催日時

12:30 ~

受講料

41,040円(税込)/人

※本文中に提示された主催者の割引は申込後に適用されます

※銀行振込

開催場所

東京都

【江戸川区】タワーホール船堀

【地下鉄】船堀駅

主催者

キーワード

半導体技術関連セミナー

もっと見る関連教材

もっと見る関連記事

もっと見る-

普通の組織をイノベーティブにする処方箋 (その174)イノベーション創出

【目次】 【この連載の前回:普通の組織をイノベーティブにする処方箋 (その173)へのリンク】 前回まで自分が生物... -

シリカ、シリコン、シリコーンの違いをわかりやすく解説

シリカ、シリコン、シリコーンこの単語、みなさんの生活の中で聞いたことがあるかと思います。みなさんは、この3つの違いがわかりますか?実は... -

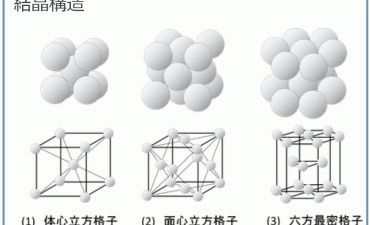

構造因子 面心立方格子:金属材料基礎講座(その134)

◆ 構造因子 面心立方格子 面心立方格子の構造因子を見てみます。面心立方格子の場合、立方格子の頂点の000と各面の中心1/2,1/2... -

リフレーミングとは、メンタルモデルを変え、新しい視点や理解を生む

清掃でメンタルモデルを変えると、職場清掃が意識改革と生産性向上をもたらします。清掃時間を通じたリフレーミングと、メンタルモデル変革を目...